总线¶

负载¶

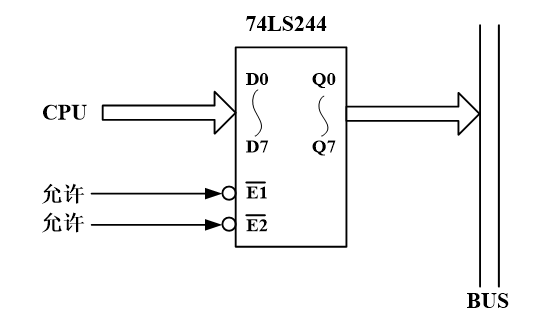

驱动¶

- 提高信号驱动能力

- 减轻总线负载

- 使用的芯片都是三态输出,使能端连地址译码电路。地址不在指定范围时,输出为高阻,相当于 CPU 和总线断开,防止总线竞争

单向¶

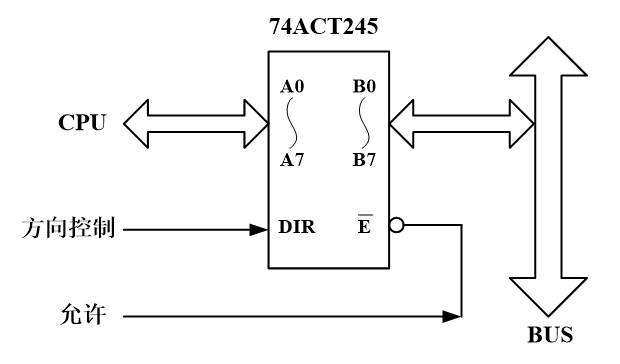

双向¶

- 当 \(\overline{E}=1\) 时,\(A,B\) 都是高阻,实现 CPU 与总线分离

- 当 \(\overline{E}=0\) 时

- \(DIR=0, B \rightarrow A\)

- \(DIR=1, A \rightarrow B\)

通常

- \(A\) 连 CPU

- \(B\) 连内存、外设

- \(DIR\) 连 \(\overline{MEMR}\) 或 \(\overline{IOR}\)

- \(\overline{E}\) 连地址译码电路,通常用 74LS138(3-8 译码器)实现

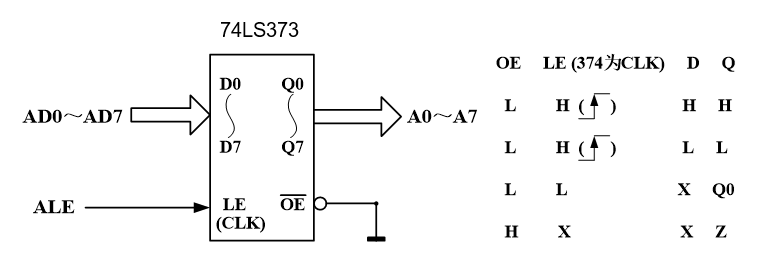

锁存¶

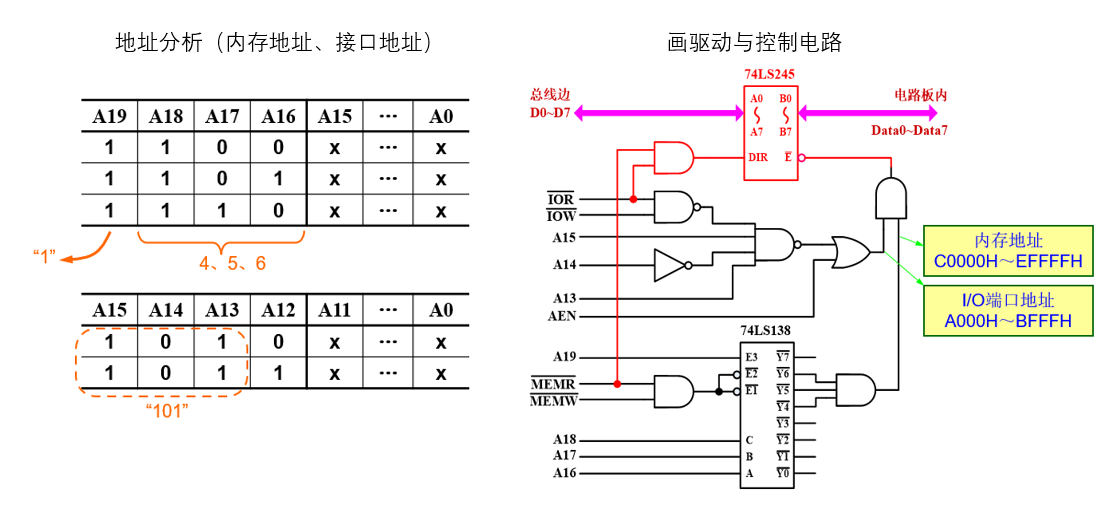

例题¶

某微型机电路板上有内存 C0000H-EFFFFH 和接口 A000H-BFFFH,试画出该电路板板内双向数据总线驱动与控制电路。

- 防止总线竞争原则:只有当 CPU 读板内内存或读板内接口时,才允许双向数据驱动器指向系统总线的三态门是导通的。