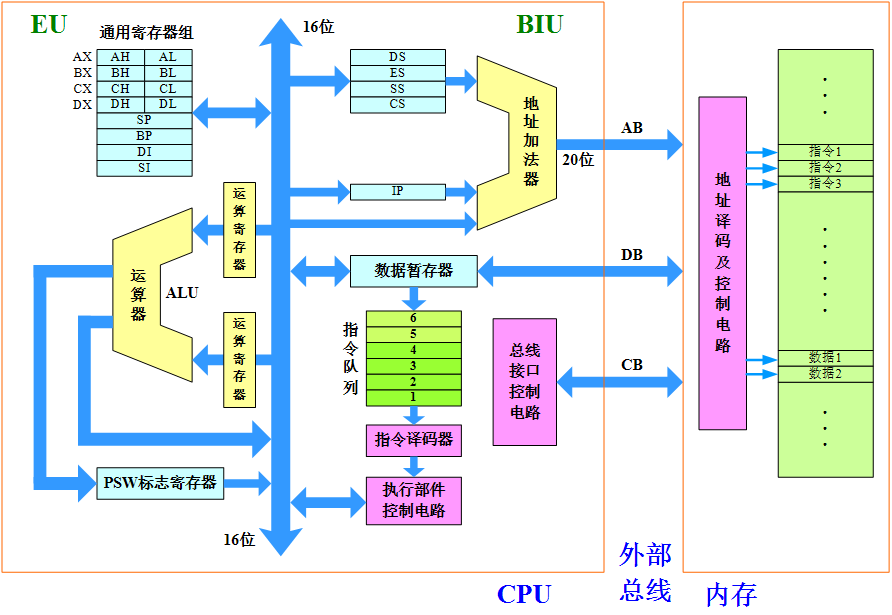

8086 和 8088 CPU¶

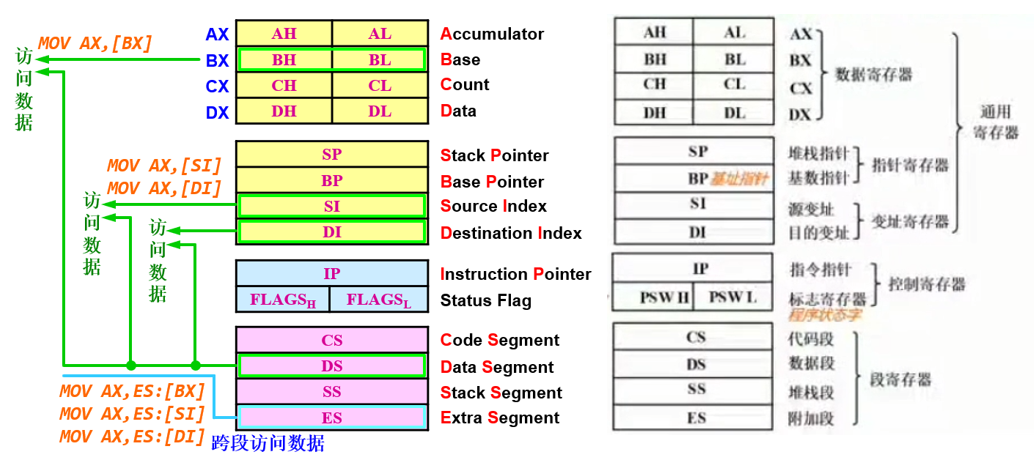

寄存器¶

通用寄存器和段寄存器¶

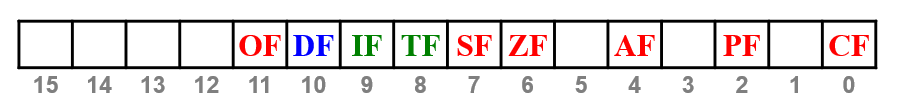

程序状态字 PSW¶

共 16 位,但只使用 9 位。

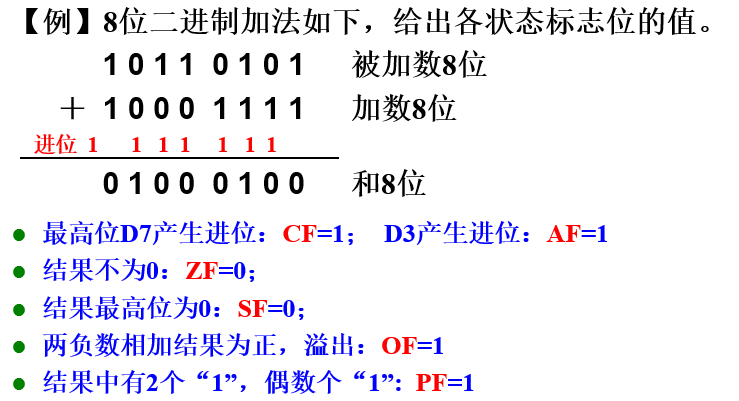

自动设置的标志位¶

| 助记 | 全称 | 全称 | 值 |

|---|---|---|---|

| AF | Auxiliary Carry Flag | 辅助进位标志位 | 如果第 3 位向第 4 位进位,则置 1。用于 BCD 加法中的加 6 修正 |

| CF | Carry Flag | 进位或借位标志位 | 最高位向更高位进位时置 1 |

| PF | Parity Flag | 奇偶标志位 | 结果有偶数个 1 时置 1 |

| SF | Sign Flag | 符号标志位 | 永远是结果的最高位 |

| ZF | Zero Flag | 零标志位 | 结果为 0 时置 1 |

| OF | Overflow Flag | 溢出标志位 | 解释为补码运算时,如果结果溢出则置 1 |

CPU 不知道运算的操作数是否有符号,只会机械地设置标志位,有无符号要靠程序员判断。例如,如果是无符号数加法,判断溢出使用 CF,有符号数用 OF。

特殊标志位¶

| 助记 | 全称 | 全称 | 作用 |

|---|---|---|---|

| DF | Direction Flag (Strings) | 方向标志位 | 控制串操作的方向,使用 STD/CLD 指令控制 |

| IF | Interrupt Enable Flag | 中断允许标志位 | 开或关中断,使用 STI/CLI 指令控制 |

| TF | Trap - Single Step Flag | 陷阱标志位 | 用于单步调试,开启后,每执行一条指令就会触发陷阱中断 |

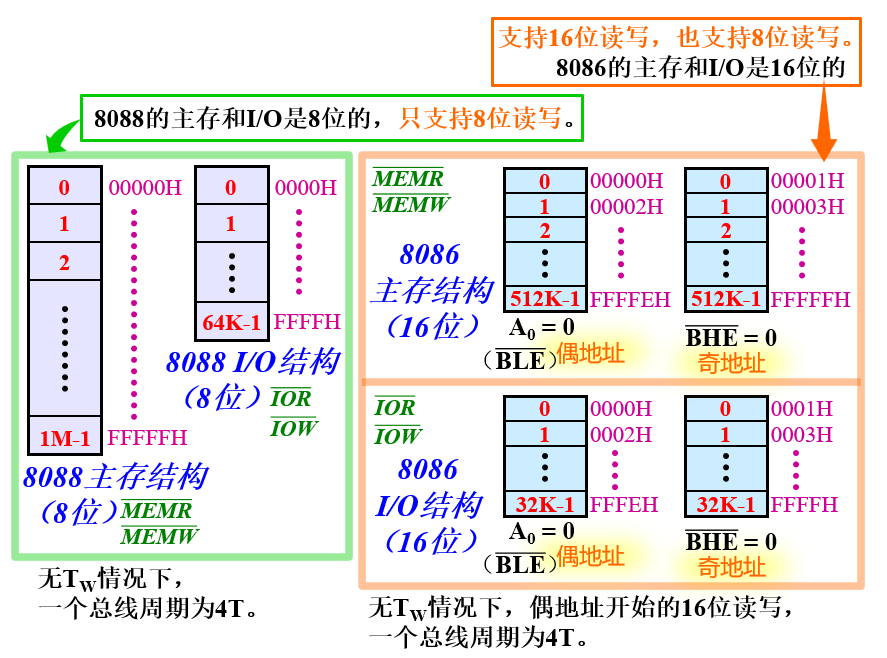

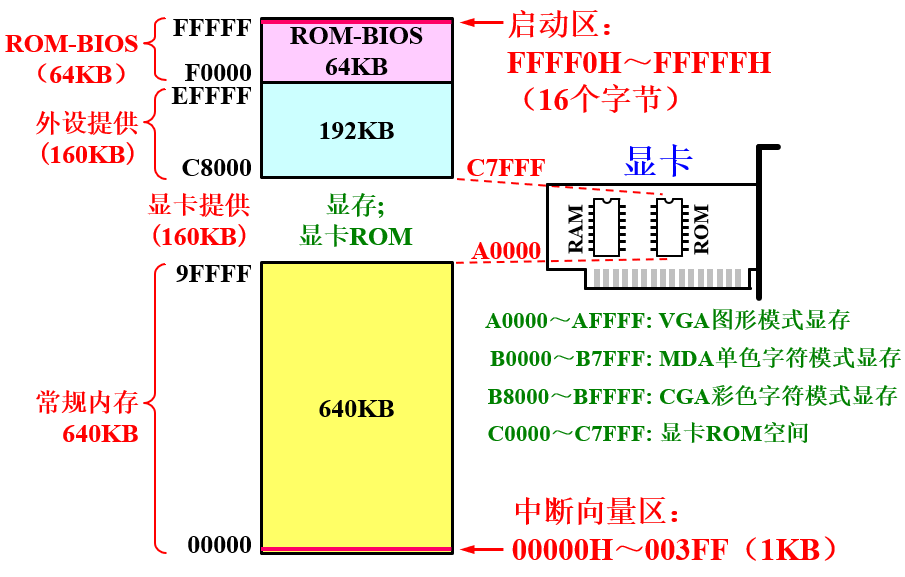

主存结构¶

- 内存和接口独立编址

- 内存分体、分段,地址 20 位(5 个 16 进制数),可寻址 1MB

- 接口分体、不分段,地址 16 位(4 个 16 进制数),可寻址 64KB

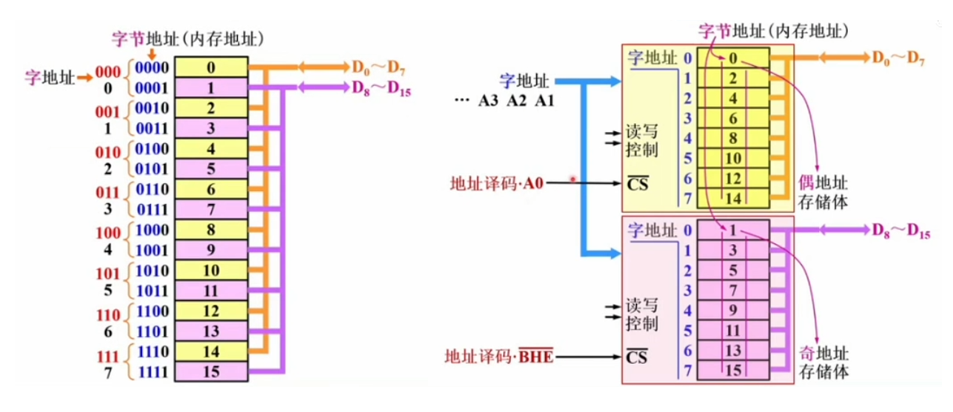

分体¶

分为奇偶两个储存体,既可以 16 位读写,也可以 8 位读写。

内存地址的最低位 \(\text{A}_0\) 作为偶地址选择信号,\(\overline{\text{BHE}}\) 作为奇地址选择信号

- 不能用 \(\overline{\text{A}_0}\) 代替 \(\overline{\text{BHE}}\) ,因为有时候会同时选中偶地址和奇地址

- 8 位读时可以不区分奇偶存储体,把不需要的字节忽略即可

- 8 位写时必须区分奇偶存储体,否则会修改不该写入的字节

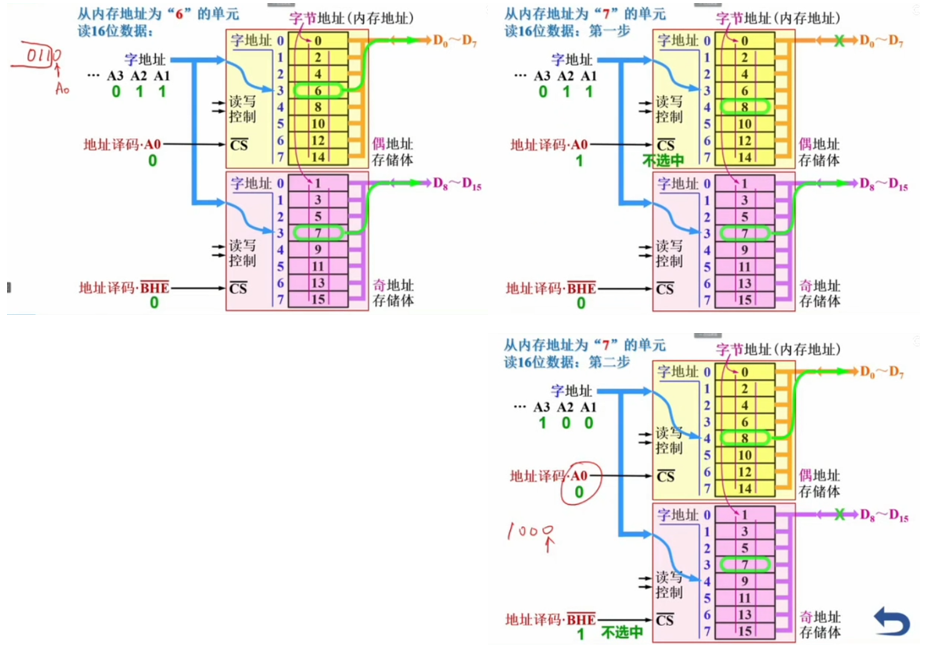

内存对齐

以读 2 字节数据为例

- 如果从地址 6 开始读两个字节(对齐),能同时选中奇偶两个存储体,一次就能读出数据

- 如果从地址 7 开始读两个字节(不对齐),第一次只能选中奇存储体,第二次再选择偶存储体,需要两次才能读出数据

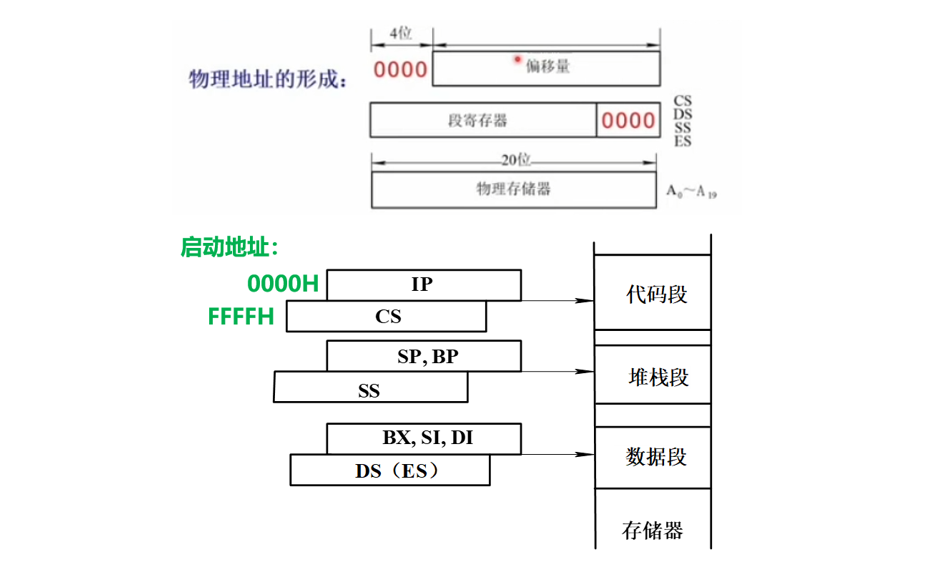

分段¶

- 各个段可以重叠

-

形式地址表示为

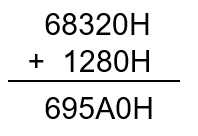

段起始地址:段内偏移,两部分都是 16 位,放在两个寄存器中。例如6832H:1280H对应物理地址为68320H + 1280H = 695A0H,注意 16 进制的段起始地址后要加一个 0

分段的优势:

- 使用可以用 16 位寻址 1MB(20 位)空间。代码、数据量不大时,将它们放在一个段中(64 KB 范围内),可以减少指令的长度,提高运行速度

- 便于程序的浮动分配

CPU 启动后复位时,CS 被初始化为 FFFFH,IP 被初始化为 0000H,所以一开始执行 FFFF0H + 0000H = FFFF0H 处的指令。但 FFFF0H ~ FFFFFH 的空间太小,通常存的是跳转指令,跳转到真正的程序。